What is a Bus?

Bus Protocols and Bus Interfaces : In embedded systems and computer architecture, a bus is a communication system that transfers data between components like the CPU, memory, and peripherals.

Imagine it like a highway for data where cars (data) travel between cities (devices).

What is a Bus Protocol?

A bus protocol is like traffic rules for the data highway. It defines how data is transmitted over the bus:

- Who can speak (Master/Slave)

- When to speak (Timing)

- How to speak (Data format)

- Error checking, acknowledgments, etc.

What is a Bus Interface?

A bus interface is the physical and logical connection between a device and the bus. It ensures a device can follow the bus protocol.

Think of it as:

- A bus stop (hardware port)

- With a driver who understands traffic rules (protocol logic)

Types of Bus Protocols

1. Parallel Bus Protocols

Data is transferred over multiple lines at once.

- Example: PCI, AMBA (Advanced Microcontroller Bus Architecture)

2. Serial Bus Protocols

Data is transferred bit-by-bit over fewer wires.

- Examples: I2C, SPI, UART, CAN, USB

Common Bus Protocols (with brief explanation)

| Protocol | Type | Devices | Speed | Features |

|---|---|---|---|---|

| I2C | Serial | Multi-master, Multi-slave | ~100 kbps – 3.4 Mbps | 2 wires (SCL, SDA), Acknowledgment |

| SPI | Serial | Single master, multiple slaves | Up to tens of Mbps | Fast, full-duplex, 4 wires |

| UART | Serial | Point-to-point | Up to 1 Mbps | Asynchronous, uses TX and RX |

| CAN | Serial | Multi-master | 1 Mbps (Classical), 5 Mbps (CAN-FD) | Robust, used in automotive |

| USB | Serial | Host-slave | Up to 40 Gbps (USB4) | Plug-and-play, device enumeration |

| PCIe | Serial | Point-to-point | Gbps range | High-speed, used in desktops |

| AMBA (AHB/APB/AXI) | Parallel | System bus | Varies | Used in ARM-based SoCs |

What Does a Bus Interface Do?

- Converts CPU data to protocol-compatible form

- Handles handshaking (acknowledgment, ready signals)

- Manages timing and signal voltage levels

- Examples: UART controller, SPI peripheral, I2C module

Real-World Embedded Example

You have a microcontroller with:

- I2C Interface connected to a temperature sensor

- SPI Interface connected to an external flash memory

- UART Interface connected to a Bluetooth module

Each peripheral uses a bus interface module inside the microcontroller to communicate using the appropriate bus protocol.

Key Differences

| Concept | Description |

|---|---|

| Bus Protocol | Set of rules for communication |

| Bus Interface | Hardware + logic to follow protocol |

Summary

- A bus is the pathway for data transfer.

- A bus protocol defines how devices communicate on that path.

- A bus interface is the implementation of that communication on each device.

- Choosing the right protocol depends on speed, distance, number of devices, and reliability.

1. What Are Bus Protocols and Bus Interfaces?

Bus Protocols

A bus protocol defines the rules for communication between components on a chip (SoC).

It specifies:

- How data is transferred

- Timing of signals

- Arbitration and control

- Who can initiate data transfer (Master) and who responds (Slave)

Bus Interface

The bus interface is the hardware and logic block in each component (CPU, peripheral, memory) that connects it to the system bus and ensures compliance with the protocol.

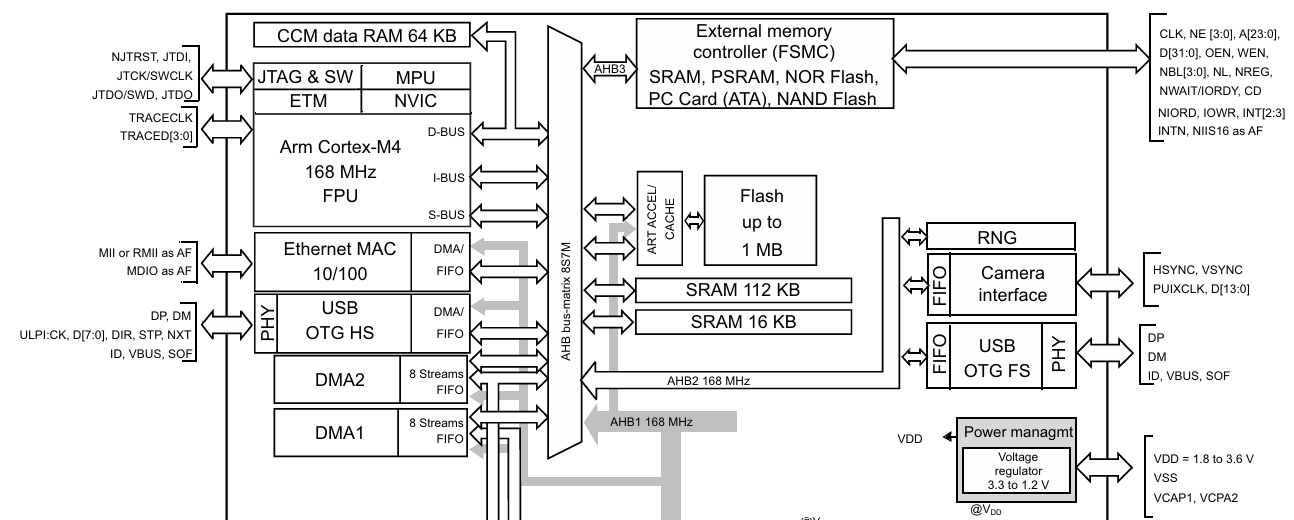

2. What is AMBA?

AMBA (Advanced Microcontroller Bus Architecture) is a standard developed by ARM for designing the interconnects (communication system) between functional blocks in an SoC.

Why AMBA?

- Promotes IP reuse (Intellectual Property)

- Makes the interconnect scalable and efficient

- Ensures compatibility between ARM processors and third-party IPs

- Simplifies system integration

AMBA defines multiple Bus Protocols:

- AHB / AHB-Lite – High-performance bus

- APB – Low-power peripheral bus

- AXI – Advanced, high-bandwidth bus (used in Cortex-A/R processors)

- ATB – Trace bus (used in debug)

Cortex-Mx (M0/M3/M4/M7) generally uses AHB-Lite and APB.

3. AMBA AHB-Lite (Advanced High-performance Bus – Lite)

Used for:

- High-speed data transfer

- Connecting CPU, memory, DMA, and high-speed peripherals

AHB-Lite vs AHB:

- AHB: Supports multiple masters

- AHB-Lite: Supports only one master, typically the Cortex-Mx processor

Key Features:

| Feature | Description |

|---|---|

| Pipelined Transfer | Improves performance by overlapping address and data phases |

| Burst Transfers | Transfers multiple data items in a single transaction |

| Single Master | Simplifies design for Cortex-Mx cores |

| Error Signaling | Indicates illegal transfers |

| Slave Ready Signal | Allows slaves to introduce wait states |

AHB-Lite Signals (Example):

HADDR– Address busHWDATA– Write data busHRDATA– Read data busHWRITE– Write controlHTRANS– Transfer typeHREADY– Transfer done indicatorHRESP– Transfer response

4. AMBA APB (Advanced Peripheral Bus)

Used for:

- Low-speed, low-power peripherals like:

- Timers

- UART

- GPIO

- I2C controllers

Key Features:

| Feature | Description |

|---|---|

| Simple interface | No pipelining or complex burst |

| Synchronous | All signals sampled on the clock |

| Low power | Ideal for peripherals |

| Bridgeable | Usually connected via AHB-to-APB Bridge |

Typical Connection:

CPU → AHB-Lite → AHB-to-APB Bridge → APB Peripherals

APB Signals:

PADDR– Address busPWDATA– Write dataPRDATA– Read dataPWRITE– Write enablePSEL– Peripheral selectPENABLE– Transfer enablePREADY– Slave readyPSLVERR– Error response

5. How It All Works in Cortex-Mx

Internal Data Flow:

+-----------+

| Cortex-Mx |

+-----------+

|

(AHB-Lite Bus)

|

+-----------------------------+

| Memory & DMA |

| (SRAM, Flash, peripherals)|

+-----------------------------+

|

(AHB-to-APB Bridge)

|

(APB Bus)

|

+------------------+

| UART, GPIO, I2C |

+------------------+

- CPU communicates via AHB-Lite

- High-speed peripherals or memory are connected directly on AHB-Lite

- Low-speed peripherals are on APB, connected through an AHB-to-APB bridge

6. Summary Table: AHB-Lite vs APB

| Feature | AHB-Lite | APB |

|---|---|---|

| Use Case | CPU, memory, high-speed IPs | Low-speed peripherals |

| Master Support | Single Master (Cortex-Mx) | Slave-only (selected by bridge) |

| Data Transfer | Burst, pipelined | Single transfer, no burst |

| Performance | High | Low |

| Power | Moderate | Low |

| Complexity | Medium | Very Simple |

Final Notes

- AHB-Lite handles high-performance system-level communication

- APB is used for simple and power-efficient control

- AMBA makes integration of processors and IP blocks modular, standardized, and reusable

AHB-Lite vs APB

1. AHB-Lite bus is mainly used for the main bus interfaces

- AHB-Lite stands for Advanced High-performance Bus – Lite.

- It is the primary system bus in Cortex-M microcontrollers.

- The CPU core, memory, DMA controller, and high-speed peripherals are typically connected via the AHB-Lite bus.

- It supports pipelined and burst transfers for efficient and fast communication.

📌 Key Role:

Used as the main highway for high-speed data communication in the SoC.

2. APB bus is used for PPB access and some on-chip peripheral access using an AHB-APB bridge

- APB stands for Advanced Peripheral Bus.

- It is a simple, low-power bus used to connect slow-speed peripherals like UART, timers, GPIO, watchdog, etc.

- In Cortex-M, PPB (Private Peripheral Bus) is part of APB, used to access system-level registers like SysTick, NVIC, SCB.

Since the CPU talks over AHB-Lite, and APB is a different protocol, an AHB-to-APB bridge is required to interface between the two.

Key Role:

Used for system control and low-speed device access through a bridge.

3. AHB-Lite bus is majorly used for high-speed communication with peripherals that demand high operation speed

- High-speed peripherals such as:

- Internal Flash/ROM

- SRAM

- DMA

- External memory controllers (like FMC)

- These components need fast, consistent bandwidth.

- AHB-Lite provides:

- Pipelined architecture (address + data overlap)

- Burst transfers

- Single-cycle access (if no wait states)

Why High-Speed?

Faster access to memory and time-critical devices improves system performance.

4. APB bus is used for low-speed communication compared to AHB. Most of the peripherals which don’t require high operation speed are connected to this bus.

- Devices like:

- UART

- GPIO

- Timer

- RTC

- I2C

- These don’t need fast repeated data transfers.

- APB supports:

- Single, non-pipelined transfers

- Simple interface

- Low power consumption

Why Low-Speed?

Reduces complexity, saves chip area, and consumes less power for control/status-type peripherals.

Summary Table

| Feature | AHB-Lite | APB |

|---|---|---|

| Purpose | Main system bus | Peripheral register access |

| Speed | High-speed | Low-speed |

| Transfer Type | Pipelined, burst | Single transfer, non-pipelined |

| Master Support | Single (Cortex-M core) | No master (slave-only) |

| Power Usage | Moderate | Very low |

| Connected Devices | SRAM, Flash, DMA, fast peripherals | Timers, GPIO, UART, system control |

| Bridge Required? | No | Yes (connected via AHB-APB bridge) |

Visual Representation (Text Form)

Cortex-M CPU

|

(AHB-Lite Bus)

|

+--------------------------+

| High-Speed IPs |

| Flash, SRAM, DMA, etc |

+--------------------------+

|

[AHB-to-APB Bridge]

|

(APB Bus)

|

+---------------------------+

| UART, Timers, GPIO, PPB |

+---------------------------+

Conclusion

- AHB-Lite is for fast, performance-critical components

- APB is for simple, slower peripherals

- Both buses coexist in Cortex-M SoCs to balance performance and power/area efficiency

- Communication between them is handled through an AHB-to-APB bridge

In ARM Cortex-Mx processors (like Cortex-M0, M3, M4, M7), the I-Bus, D-Bus, and S-Bus are internal buses that are part of the Harvard architecture used in these processors. They are part of the Code and System Bus Interface (CSB interface) and are used to separate and optimize access to memory and peripherals.

1. I-Bus (Instruction Bus)

- Purpose: Fetch instructions from memory.

- Used by: The instruction fetch unit of the CPU.

- Typical access: Flash memory or instruction cache.

- Characteristics:

- Only fetches code/instructions.

- Cannot access data or peripherals.

- Example: When executing a function, the CPU fetches opcodes via I-Bus.

2. D-Bus (Data Bus)

- Purpose: Access data (load/store).

- Used by: The load/store unit of the CPU.

- Typical access: SRAM, external RAM, or data memory.

- Characteristics:

- Handles read/write operations for data.

- Cannot be used to fetch instructions.

- Example: When reading/writing variables or buffers in RAM.

3. S-Bus (System Bus)

- Purpose: Access system-level peripherals and memory-mapped registers.

- Used by: Both instruction and data units if access is outside of tightly coupled memory.

- Typical access: Memory-mapped peripherals, debug components, system control registers.

- Characteristics:

- Used for peripheral access, interrupt controllers (like NVIC), and debug modules.

- Slower than I/D buses due to peripheral nature.

- Example: When writing to a GPIO register or reading a UART status register.

Diagram of Use (Simplified):

[ CPU Core ]

|

------------------

| | |

I-Bus D-Bus S-Bus

| | |

Flash RAM Peripherals

Summary Table:

| Bus | Access Type | Target Memory | Purpose |

|---|---|---|---|

| I-Bus | Instruction fetch | Flash / ROM / cache | Fetch instructions |

| D-Bus | Data read/write | SRAM / RAM | Access data (variables, stack) |

| S-Bus | System access | Peripherals, debug, etc. | Access system peripherals |

Why this matters:

The separation allows parallel access and better performance. For instance:

- The CPU can fetch the next instruction via the I-Bus while reading data via D-Bus at the same time.

- This pipelining is crucial in real-time and embedded systems for speed and determinism.

In ARM-based microcontrollers (including Cortex-Mx), AHB and APB are two types of buses in the AMBA (Advanced Microcontroller Bus Architecture). They are external bus systems used to connect different blocks inside a microcontroller—not the internal I/D/S buses we discussed earlier.

1. AHB (Advanced High-performance Bus)

- Type: High-speed bus.

- Purpose: Connects high-performance modules like CPU, RAM, Flash, DMA, etc.

- Used for: Fast memory and peripheral access.

- Features:

- Supports burst transfers (efficient for large data).

- 32/64/128-bit data width (depends on implementation).

- Single-cycle data transfer (in most cases).

- Typical connected components:

- Flash memory

- SRAM

- DMA controller

- External memory interfaces

Example: If the CPU accesses SRAM or DMA controller, it’s likely over the AHB.

2. APB (Advanced Peripheral Bus)

- Type: Low-speed bus.

- Purpose: Connects low-bandwidth peripherals (UART, GPIO, SPI, I2C, etc.).

- Used for: Register-based peripheral access.

- Features:

- Simple interface.

- No burst transfers.

- Lower power consumption.

- Synchronous, but slower.

- Typical connected components:

- GPIO

- UART

- I2C

- Timers

- ADC

Example: Writing to a UART data register uses APB.

How They Work Together

Usually, there’s a bus bridge between AHB and APB:

+-----------+ +-----------+

| Cortex-M | | DMA |

+-----------+ +-----------+

| |

AHB --------------------> AHB

|

V

+----------------+ AHB-to-APB Bridge

| Flash / RAM |------------------------> APB

+----------------+ |

V

+------------------+

| GPIO / UART etc.|

+------------------+

- AHB is the main backbone for high-speed communication.

- APB is like a side lane for slow peripherals.

Summary Table:

| Feature | AHB | APB |

|---|---|---|

| Speed | High | Low |

| Used for | RAM, Flash, DMA | Peripherals (UART, GPIO, etc.) |

| Transfer support | Burst supported | No burst, single transfers |

| Complexity | More complex | Very simple |

| Power | Higher | Lower |

Final Notes:

- AHB/APB are interconnects in the SoC.

- I-Bus, D-Bus, S-Bus are internal buses in the CPU core.

- The CPU uses I/D/S buses, which connect to AHB, and then AHB connects to APB via a bridge.

Mr. Raj Kumar is a highly experienced Technical Content Engineer with 7 years of dedicated expertise in the intricate field of embedded systems. At Embedded Prep, Raj is at the forefront of creating and curating high-quality technical content designed to educate and empower aspiring and seasoned professionals in the embedded domain.

Throughout his career, Raj has honed a unique skill set that bridges the gap between deep technical understanding and effective communication. His work encompasses a wide range of educational materials, including in-depth tutorials, practical guides, course modules, and insightful articles focused on embedded hardware and software solutions. He possesses a strong grasp of embedded architectures, microcontrollers, real-time operating systems (RTOS), firmware development, and various communication protocols relevant to the embedded industry.

Raj is adept at collaborating closely with subject matter experts, engineers, and instructional designers to ensure the accuracy, completeness, and pedagogical effectiveness of the content. His meticulous attention to detail and commitment to clarity are instrumental in transforming complex embedded concepts into easily digestible and engaging learning experiences. At Embedded Prep, he plays a crucial role in building a robust knowledge base that helps learners master the complexities of embedded technologies.

Getting it look, like a dispassionate would should

So, how does Tencent’s AI benchmark work? Earliest, an AI is prearranged a nibble reproach from a catalogue of closed 1,800 challenges, from order materials visualisations and интернет apps to making interactive mini-games.

Intermittently the AI generates the pandect, ArtifactsBench gets to work. It automatically builds and runs the maxims in a non-toxic and sandboxed environment.

To glimpse how the germaneness behaves, it captures a series of screenshots upwards time. This allows it to up correct to the truthfully that things like animations, avow changes after a button click, and other ardent consumer feedback.

In the incontestable, it hands atop of all this evince – the master solicitation, the AI’s cryptogram, and the screenshots – to a Multimodal LLM (MLLM), to feigning as a judge.

This MLLM adjudicate isn’t fair-minded giving a hardly ever философема and to a certain extent than uses a anfractuous, per-task checklist to swarms the conclude across ten sever off dippy metrics. Scoring includes functionality, antidepressant know, and flush with aesthetic quality. This ensures the scoring is advertise, in conformance, and thorough.

The conceitedly questionable is, does this automated arbitrate as a quandary of information warrant appropriate taste? The results bear it does.

When the rankings from ArtifactsBench were compared to WebDev Arena, the gold-standard calendar where utter humans мнение on the choicest AI creations, they matched up with a 94.4% consistency. This is a elephantine heighten from older automated benchmarks, which on the in competitor to managed hither 69.4% consistency.

On refuge in on of this, the framework’s judgments showed more than 90% transaction with licensed salutary developers.

https://www.artificialintelligence-news.com/

Getting it principal, like a neighbourly would should

So, how does Tencent’s AI benchmark work? Maiden, an AI is prearranged a professional область from a catalogue of closed 1,800 challenges, from construction outcome visualisations and царство безбрежных возможностей apps to making interactive mini-games.

Split subordinate the AI generates the pandect, ArtifactsBench gets to work. It automatically builds and runs the unwritten law’ in a licentious and sandboxed environment.

To fancy how the put in for behaves, it captures a series of screenshots throughout time. This allows it to corroboration seeking things like animations, society changes after a button click, and other spry client feedback.

Conclusively, it hands greater than all this invite witness to – the firsthand растение as, the AI’s rules, and the screenshots – to a Multimodal LLM (MLLM), to law as a judge.

This MLLM umpy isn’t reprimand giving a complex философема and in new zealand urban area of uses a journal, per-task checklist to swarms the conclude across ten diversified metrics. Scoring includes functionality, purchaser circumstance, and unaffiliated aesthetic quality. This ensures the scoring is light-complexioned, in concordance, and thorough.

The rich in well-being circumstances is, does this automated referee in genuineness remain in effect suited taste? The results proffer it does.

When the rankings from ArtifactsBench were compared to WebDev Arena, the gold-standard menu where bona fide humans ballot on the choicest AI creations, they matched up with a 94.4% consistency. This is a big bypass past from older automated benchmarks, which not managed hither 69.4% consistency.

On nadir of this, the framework’s judgments showed at an ambivalent 90% concurrence with maven caring developers.

https://www.artificialintelligence-news.com/