Master Microprocessor Interview Questions with this comprehensive guide covering beginner to senior-level MPU concepts, interrupts, pipelining, memory management, and embedded systems. Perfect for freshers, experienced engineers, and embedded professionals preparing for interviews.

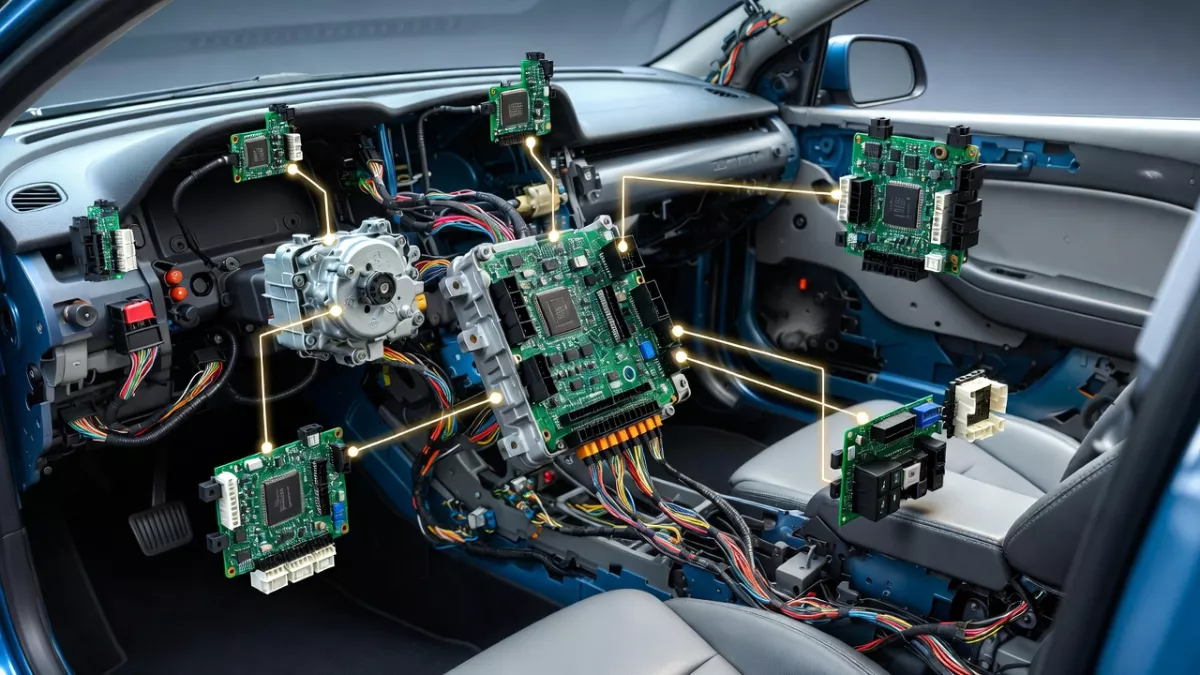

Microprocessors are the heart of modern computing and embedded systems, making them a critical topic for technical interviews, especially for embedded software engineers. This comprehensive Microprocessor Interview Question guide covers everything from beginner to senior-level questions, designed to help freshers, early-career engineers, and experienced professionals prepare thoroughly.

For beginners, questions focus on understanding the basics: what a microprocessor is, its components, instruction sets, registers, buses, memory types, and interrupt fundamentals. These questions ensure candidates grasp core concepts like how data flows inside a CPU, how instructions are executed, and how peripherals interact with the processor.

At the intermediate level, the questions delve deeper into architecture, addressing modes, instruction execution, pipelining, memory management, and detailed interrupt handling. Interviewers use these questions to evaluate a candidate’s ability to understand system design, performance optimization, and real-world embedded applications.

For advanced candidates, questions focus on performance metrics, pipeline hazards, cache memory, virtual memory, low-level CPU operations, and embedded system optimization. These help assess problem-solving skills, debugging capabilities, and knowledge of microprocessor internals critical for high-performance systems.

At the experienced/senior level, the questions move toward system-level design, real-time constraints, embedded Linux, RTOS, and scenario-based problem-solving. These evaluate a candidate’s ability to design, debug, and optimize complex microprocessor-based systems, including considerations for power, performance, and latency.

This guide also includes bonus frequently asked questions on DSP, ARM architecture, real-time systems, and cross-compilation, helping candidates stand out in competitive interviews.

By going through this structured question list, candidates not only prepare for interviews but also gain practical understanding of how microprocessors work in real embedded systems, bridging the gap between theory and hands-on applications.

This makes it a must-read for anyone aiming to excel in embedded software, electronics design, and system-level engineering roles.

BEGINNER LEVEL (0–1 Year | Freshers)

Basics of Microprocessor

- What is a microprocessor?

- Difference between microprocessor and microcontroller.

- What are the main components of a microprocessor?

- What is an instruction set?

- What is machine language?

- What is assembly language?

- What is opcode?

- What is operand?

- What is word length in a microprocessor?

- What is clock frequency?

- What is throughput?

- What is execution time?

- What is instruction cycle?

- What are registers?

- What is accumulator?

- What is Program Counter (PC)?

- What is Stack Pointer (SP)?

- What is Instruction Register (IR)?

- What is Flag Register?

- What are status flags?

Memory & Bus Basics

- What is address bus?

- What is data bus?

- What is control bus?

- Difference between address bus and data bus.

- What is memory?

- Difference between ROM and RAM.

- What is cache memory?

- Why cache is faster than RAM?

- What is memory addressing?

- What is addressable memory?

Interrupt Basics

- What is an interrupt?

- Why interrupts are used?

- Types of interrupts.

- Difference between hardware and software interrupt.

- What is interrupt latency?

- What is ISR (Interrupt Service Routine)?

- What is polling?

INTERMEDIATE LEVEL (1–3 Years)

Architecture & Internal Working

- Explain microprocessor architecture.

- What is pipelining?

- Advantages of pipelining.

- What is RISC architecture?

- What is CISC architecture?

- Difference between RISC and CISC.

- What is Harvard architecture?

- What is Von Neumann architecture?

- Difference between Harvard and Von Neumann.

- What is superscalar architecture?

- What is multi-core processor?

- What is hyper-threading?

- What is instruction-level parallelism?

Addressing Modes

- What is addressing mode?

- Types of addressing modes.

- Immediate addressing mode.

- Direct addressing mode.

- Indirect addressing mode.

- Register addressing mode.

- Indexed addressing mode.

- Relative addressing mode.

- Base addressing mode.

- Stack addressing mode.

Instruction Set & Execution

- What are arithmetic instructions?

- What are logical instructions?

- What are control instructions?

- What are data transfer instructions?

- What is branching instruction?

- What is conditional branching?

- What is subroutine?

- Difference between CALL and JMP.

- What is stack?

- Why stack grows downward?

Interrupts (Detailed)

- Maskable vs Non-maskable interrupt.

- What is interrupt priority?

- What is interrupt vector table?

- What is nested interrupt?

- What is vectored interrupt?

- What is non-vectored interrupt?

- How does microprocessor handle an interrupt?

- What happens internally when interrupt occurs?

- Difference between polling and interrupt.

- How interrupt improves CPU utilization?

I/O & Peripherals

- What is I/O mapped I/O?

- What is memory-mapped I/O?

- Difference between I/O mapped and memory-mapped I/O.

- What is DMA?

- Why DMA is required?

- What is DMA controller?

- What is handshaking?

- What is wait state?

- What is bus arbitration?

- What is tri-state buffer?

ADVANCED LEVEL (3–5 Years)

Performance & Optimization

- What factors affect microprocessor performance?

- What is CPI (Cycles Per Instruction)?

- What is MIPS?

- What is FLOPS?

- What is cache coherence?

- What is cache hit and miss?

- What is cache associativity?

- Direct-mapped vs associative cache.

- What is write-through cache?

- What is write-back cache?

Memory Management

- What is virtual memory?

- What is paging?

- What is segmentation?

- Difference between paging and segmentation.

- What is TLB?

- What is page fault?

- What is memory protection?

- What is MMU?

- How address translation works?

- What is physical vs virtual address?

Pipeline & Hazards

- What is pipeline hazard?

- Types of pipeline hazards.

- What is data hazard?

- What is control hazard?

- What is structural hazard?

- What is branch prediction?

- Static vs dynamic branch prediction.

- What is speculative execution?

- What is instruction reordering?

- What is out-of-order execution?

Low-Level & Embedded View

- Difference between microprocessor and SoC.

- What is bootloader?

- What happens after power-on reset?

- What is reset vector?

- What is exception handling?

- Difference between interrupt and exception.

- What is privilege mode?

- User mode vs Kernel mode.

- What is context switching?

- What registers are saved during context switch?

EXPERIENCED / SENIOR LEVEL (5+ Years)

System-Level & Real-World

- How do you select a microprocessor for a product?

- Power vs performance trade-offs.

- How microprocessor handles real-time constraints?

- How cache affects real-time systems?

- What is deterministic execution?

- How interrupts affect system latency?

- How to debug microprocessor-level issues?

- Tools used for debugging (JTAG, GDB, Trace).

- How do you optimize ISR execution time?

- How do you reduce boot time?

Advanced Memory & CPU Design

- What is NUMA architecture?

- What is SMP?

- Difference between SMP and AMP.

- What is cache line?

- False sharing problem.

- What is bus snooping?

- What is MESI protocol?

- What is instruction cache vs data cache?

- What is prefetching?

- What is memory barrier?

Embedded Linux / RTOS Perspective

- How microprocessor boots Linux?

- Role of bootloader, kernel, init.

- How interrupts are handled in Linux?

- What is IRQ vs FIQ?

- What is softirq?

- What is task scheduling?

- How context switch happens?

- Difference between process and thread.

- What is priority inversion?

- How microprocessor supports RTOS scheduling?

Scenario-Based Questions

- CPU usage is 100%, how will you debug?

- Interrupt storm issue – how to fix?

- System hangs randomly – approach?

- Cache-related bug – how to identify?

- Memory corruption – debugging steps?

- ISR taking too long – optimization?

- DMA vs CPU copy – when to choose?

- How to design low-power system?

- Handling high-frequency interrupts?

- Debugging boot failure at reset stage?

BONUS

- Difference between microprocessor and DSP.

- Why ARM dominates embedded systems?

- Why RISC is preferred in embedded?

- What is real-time system?

- Hard real-time vs soft real-time.

- What is bare-metal programming?

- What is cross-compilation?

- How compiler interacts with microprocessor?

- What is ABI?

- What is endianness?

ARM CORTEX-M4 INTERVIEW QUESTIONS

SECTION 1: ARM BASICS & INTRODUCTION

- What is ARM?

- What is ARM Cortex?

- What is ARM Cortex-M series?

- Difference between Cortex-M0, M3, M4, M7

- Where is Cortex-M4 used?

- What does “Thumb-2” mean?

- Why ARM uses RISC architecture?

- Harvard vs Modified Harvard architecture

- What is ARMv7-M architecture?

- What is ARM license model?

SECTION 2: CORTEX-M4 CORE ARCHITECTURE

- Explain Cortex-M4 block diagram

- What is pipeline in Cortex-M4?

- Number of pipeline stages

- What is single-cycle I/O?

- What is fetch–decode–execute?

- What is core register file?

- List general-purpose registers (R0–R12)

- Special registers in Cortex-M4

- What is PC?

- What is LR?

- What is SP?

- MSP vs PSP

- When MSP is used?

- When PSP is used?

- What is xPSR?

- APSR, IPSR, EPSR difference

- What is CONTROL register?

- What is privilege mode?

- Thread mode vs Handler mode

- User mode vs Privileged mode

SECTION 3: INSTRUCTION SET & PROGRAMMING

- What is Thumb instruction set?

- Thumb vs ARM instruction set

- Why Cortex-M supports only Thumb?

- What is Thumb-2?

- Instruction alignment rules

- Load/store architecture

- What are barrel shifters?

- What are conditional instructions?

- What is IT block?

- What is NOP instruction?

- What is BKPT instruction?

- What is WFI?

- What is WFE?

- Difference between WFI and WFE

- What is SVC instruction?

- What is CPSID / CPSIE?

- What is CLZ instruction?

- What is MUL instruction?

- What is MAC instruction?

- What instructions are atomic?

SECTION 4: MEMORY ARCHITECTURE

- Cortex-M4 memory map

- Code region address range

- SRAM region address range

- Peripheral region

- System control space (SCS)

- Bit-banding concept

- SRAM bit-banding

- Peripheral bit-banding

- Advantages of bit-banding

- What is memory alias region?

- What is memory alignment?

- Unaligned access support?

- What is little-endian?

- Does Cortex-M4 support big-endian?

- What is memory barrier?

- DMB, DSB, ISB difference

- What is strongly ordered memory?

- What is device memory?

- What is normal memory?

- What is MPU?

SECTION 5: STACK & FUNCTION CALL MECHANISM

- What is stack?

- Full descending stack meaning

- Stack frame in Cortex-M

- What registers are stacked automatically?

- Hardware stacking during interrupt

- Software stacking vs hardware stacking

- Stack alignment rule

- What is EXC_RETURN?

- How return from interrupt happens?

- What is tail-chaining?

- What is late-arrival interrupt?

- How stack overflow occurs?

- How to detect stack overflow?

- MSP usage during reset

- PSP usage in RTOS

SECTION 6: INTERRUPT & EXCEPTION SYSTEM (NVIC)

- What is NVIC?

- How many interrupts supported?

- Interrupt priority levels

- Preemption priority vs sub-priority

- Priority grouping

- What is vector table?

- Reset vector

- Exception types in Cortex-M4

- Difference between exception and interrupt

- NMI interrupt

- HardFault

- MemManage fault

- BusFault

- UsageFault

- SVCall

- PendSV

- SysTick

- Fault escalation

- Nested interrupt handling

- Interrupt latency

- How priority works internally?

- What is BASEPRI?

- What is PRIMASK?

- What is FAULTMASK?

- How to disable interrupts safely?

SECTION 7: SYSTICK TIMER

- What is SysTick?

- Why SysTick is used?

- SysTick clock source

- SysTick register set

- SysTick interrupt interval calculation

- SysTick vs hardware timer

- SysTick in RTOS

- Tickless mode

- SysTick priority

- SysTick overflow behavior

SECTION 8: MPU (MEMORY PROTECTION UNIT)

- What is MPU?

- Why MPU is needed?

- Number of MPU regions

- MPU region size rules

- Overlapping regions

- MPU access permissions

- Privileged vs unprivileged access

- Execute-Never (XN)

- MPU configuration steps

- MPU faults

- Difference between MPU and MMU

- MPU in RTOS

- MPU for task isolation

- MPU impact on performance

- Common MPU mistakes

SECTION 9: DSP & FPU (CORTEX-M4 SPECIAL)

- What DSP features exist in M4?

- SIMD instructions

- Saturation arithmetic

- MAC instructions

- Q-format fixed-point math

- What is FPU?

- Single-precision FPU

- Lazy stacking

- FPU context save

- Hard vs soft float

- Compiler flags for FPU

- FPU registers

- Impact of FPU on ISR

- DSP vs FPU

- When to avoid FPU?

SECTION 10: CLOCK, POWER & LOW POWER MODES

- Clock tree concept

- Core clock vs peripheral clock

- Sleep mode

- Deep sleep mode

- Standby mode

- What is WFI used for?

- What wakes CPU from sleep?

- Power consumption factors

- Dynamic frequency scaling

- Clock gating

- Brown-out reset

- Reset sources

- Startup time

- Low-power ISR handling

- Debug in low-power mode

SECTION 11: BOOT PROCESS & STARTUP

- What happens after reset?

- Role of startup file

- Vector table initialization

- Stack initialization

- Data section initialization

- BSS section

- Linker script role

- Reset handler flow

- SystemInit() role

- Relocating vector table

- Bootloader vs application

- Jumping to application

- Secure boot concept

- Firmware update process

- Common boot failures

SECTION 12: DEBUGGING & FAULT ANALYSIS

- Debug interface (SWD/JTAG)

- What is SWD?

- Breakpoints types

- Hardware vs software breakpoint

- Watchpoints

- ITM

- DWT

- Trace features

- HardFault debugging steps

- Reading fault registers

- Common HardFault reasons

- Stack corruption detection

- Instruction fetch fault

- Bus fault debugging

- Debugging optimized code

- Debug vs release behavior

- Semihosting

- GDB with Cortex-M

- Core registers inspection

- Crash dump analysis

SECTION 13: RTOS & REAL-TIME CONCEPTS

- How RTOS runs on Cortex-M4?

- Context switching mechanism

- Role of PendSV

- SysTick vs PendSV

- Task stack vs MSP

- Priority inversion

- Mutex vs semaphore

- ISR safe APIs

- Critical section handling

- Preemptive scheduling

- Round robin scheduling

- Tick rate selection

- RTOS latency sources

- Determinism in Cortex-M

- Hard real-time handling

SECTION 14: PERFORMANCE & OPTIMIZATION

- Code optimization techniques

- Cache availability in M4?

- Branch penalty

- Loop unrolling

- Inline functions

- DMA vs CPU copy

- ISR optimization techniques

- Memory placement optimization

- Use of volatile

- Alignment optimization

- Linker-based optimization

- FPU optimization tips

- DSP instruction usage

- Power vs performance trade-off

- Measuring execution time

SECTION 15: REAL INTERVIEW SCENARIOS

- HardFault occurs randomly — approach?

- ISR nesting issue — debug?

- Stack overflow in RTOS — fix?

- Missed interrupts — reason?

- High CPU load — analysis?

- Low-power mode not waking — debug?

- Boot stuck before main()

- DMA corrupting memory

- Priority inversion issue

- Latency critical system design

- How to design safety-critical system?

- How to handle firmware upgrade safely?

- How to ensure MISRA compliance?

- Handling EMI related crashes

- Field failure debugging

FINAL BONUS (ABSOLUTE MUST-KNOW)

- Cortex-M vs Cortex-A

- Cortex-M vs DSP

- Why Cortex-M4 is popular?

- Automotive use of Cortex-M4

- Safety standards (ISO 26262)

- TrustZone support?

- Secure vs non-secure world

- Common beginner mistakes

- Common senior-level mistakes

- How interviewers judge Cortex-M knowledge?

ARM Cortex-M4 Booting Process

1. Power-On / Reset Event

Booting starts when any reset source occurs:

- Power-On Reset (POR)

- External Reset pin

- Watchdog reset

- Software reset

- Brown-out reset

At this moment:

- CPU is in Thread mode

- Privileged mode

- Using MSP (Main Stack Pointer)

2. CPU Fetches Vector Table

After reset, Cortex-M4 automatically reads the vector table from a fixed address.

Default Vector Table Address

0x00000000

(Internally mapped to Flash memory)

3. First Two Vector Table Entries

| Address | Content |

|---|---|

0x00000000 | Initial MSP value |

0x00000004 | Reset Handler address |

What CPU Does Automatically:

- Loads MSP from address

0x00000000 - Loads PC with Reset_Handler address

- Starts executing Reset_Handler

This happens without any software code

4. Reset Handler Execution Begins

Reset Handler is written in startup assembly file

(example: startup_stm32f407xx.s)

Typical Reset Handler Flow:

Reset_Handler:

LDR SP, =_estack

BL SystemInit

BL __libc_init_array

BL main

5. Stack Initialization

- MSP is set to top of SRAM

- Stack grows downward

- Stack alignment = 8 bytes

👉 Interview tip:

Cortex-M uses full descending stack

6. SystemInit() Function

Provided by CMSIS

What SystemInit() Does:

- Configure system clock (PLL, HSE/HSI)

- Enable FPU (if present)

- Setup Flash latency

- Configure bus prescalers

- Initialize low-level hardware

📌 Runs before main()

7. Memory Initialization (CRT Startup)

Handled by C runtime startup code

Two Critical Sections:

.data section

- Initialized global/static variables

- Copied from Flash → SRAM

.bss section

- Uninitialized globals

- Set to zero

Example:

int a = 10; // .data

int b; // .bss

8. C++ Constructor Initialization (if C++)

__libc_init_array();

- Calls global/static constructors

- Required for C++ projects

9. Vector Table Setup (Optional Relocation)

Vector table can be moved to:

- SRAM

- Another Flash location

Using:

SCB->VTOR = new_address;

Used in:

- Bootloaders

- RTOS

- Firmware update systems

10. main() Function Execution

Finally:

int main(void)

{

while(1)

{

// Application code

}

}

🎉 System is now running

11. Interrupt Handling After Boot

When interrupt occurs:

- CPU switches to Handler mode

- Uses MSP

- Automatically stacks:

- R0–R3

- R12

- LR

- PC

- xPSR

- Jumps to ISR

12. Faults During Boot (Very Important)

Common Boot Faults:

| Fault | Reason |

|---|---|

| HardFault | Bad stack address |

| UsageFault | Invalid instruction |

| BusFault | Invalid memory access |

| MemManage | MPU violation |

👉 Most boot failures happen before main()

13. Bootloader vs Application (Interview Favorite)

Bootloader:

- Small program at Flash start

- Handles:

- Firmware update

- Application validation

- Jump to application

Application:

- Actual product firmware

- Starts at offset (e.g.,

0x08004000)

Jumping to Application Steps:

- Deinit peripherals

- Set MSP

- Set VTOR

- Jump to reset handler

14. Secure Boot (Concept)

- Verify firmware signature

- Prevent unauthorized code execution

- Used in automotive & medical

15. Boot Time Optimization

- Reduce clock setup time

- Skip unused init

- Use fast internal oscillator

- Minimize constructors

- Place critical code in SRAM

BOOT FLOW DIAGRAM (INTERVIEW READY)

Reset

↓

Fetch MSP from 0x00000000

↓

Fetch Reset_Handler from 0x00000004

↓

Initialize Stack

↓

SystemInit()

↓

.data copy

↓

.bss zero

↓

C/C++ init

↓

main()

MOST ASKED INTERVIEW QUESTIONS

1.What runs before main()?

Reset_Handler and startup code

2.Who initializes stack?

Hardware loads MSP, startup code confirms

3.Why .data copied to RAM?

RAM is writable, Flash is not

4.Can main() return?

No — leads to undefined behavior

5.Why HardFault before main()?

Stack or clock misconfiguration

You now fully understand:

- Cortex-M4 boot internals

- Startup code

- Linker role

- Stack & vector table

- Real interview traps

Conclusion

Preparing for microprocessor interviews requires a solid understanding of both theory and practical system-level concepts. This structured list, covering beginner to senior-level questions, equips candidates with the knowledge to answer questions confidently and think critically about real-world embedded systems.

By mastering these questions, you not only improve your chances in interviews but also gain a deeper understanding of how microprocessors operate, interact with memory and peripherals, handle interrupts, and optimize performance. For embedded engineers, this knowledge is essential to design efficient, reliable, and high-performing systems.

Ultimately, consistent practice with these questions helps you bridge the gap between academic learning and industry expectations, making you a strong candidate for roles in embedded software, system design, and microprocessor-based development.

FAQ : MICROPROCESSOR INTERVIEW QUESTIONS

1. What is a microprocessor and why is it important in embedded systems?

A microprocessor is the central processing unit (CPU) on a single chip that executes instructions, performs calculations, and controls peripherals. It’s the heart of embedded systems, enabling devices like IoT gadgets, smartphones, and industrial controllers to function efficiently.

2. How is a microprocessor different from a microcontroller?

A microprocessor requires external memory and I/O devices to function, whereas a microcontroller integrates CPU, memory, and peripherals on a single chip. This makes microcontrollers ideal for compact embedded applications.

3. What are the main components of a microprocessor?

Key components include the ALU (Arithmetic Logic Unit), registers, control unit, program counter, and buses (data, address, and control). These components work together to execute instructions and manage data flow.

4. What is an instruction set and why is it important?

An instruction set is a collection of commands that a microprocessor can execute. It defines how software communicates with hardware and is crucial for programming and optimizing embedded applications.

5. What are interrupts and how do they improve CPU efficiency?

Interrupts allow the CPU to respond immediately to external or internal events, reducing idle time and enabling faster processing. They are critical in real-time and embedded systems for handling sensors, timers, or communication interfaces.

6. What is pipelining in a microprocessor?

Pipelining is a technique where multiple instructions are overlapped in execution stages to improve performance. It increases CPU throughput and is a common feature in modern processors.

7. What is the difference between RISC and CISC architectures?

RISC (Reduced Instruction Set Computing) uses simple, fast instructions, while CISC (Complex Instruction Set Computing) supports complex instructions. RISC is preferred in embedded systems for efficiency, power, and speed.

8. What is cache memory and why is it faster than RAM?

Cache is a small, high-speed memory inside or near the CPU that stores frequently used data. Its proximity to the processor allows much faster access compared to main RAM, improving system performance.

9. How do microprocessors handle real-time constraints?

Microprocessors manage real-time tasks using interrupts, prioritization, and deterministic execution. In RTOS-based systems, scheduling ensures critical tasks meet strict timing requirements.

10. What is the difference between memory-mapped I/O and I/O-mapped I/O?

Memory-mapped I/O uses the same address space for memory and peripherals, whereas I/O-mapped I/O uses a separate address space for devices. Memory-mapped I/O simplifies programming and is common in modern embedded systems.

11. How do DMA and CPU-based data transfer differ?

DMA (Direct Memory Access) allows peripherals to transfer data directly to memory without CPU involvement, freeing the CPU for other tasks. CPU-based transfers require the processor to move data manually, which can be slower.

12. Why is understanding microprocessor architecture critical for embedded engineers?

Understanding architecture helps engineers design efficient, low-power, and high-performance systems, optimize software for hardware, debug issues, and select the right processor for a specific application.

Read More : Char Driver Model in Linux

Mr. Raj Kumar is a highly experienced Technical Content Engineer with 7 years of dedicated expertise in the intricate field of embedded systems. At Embedded Prep, Raj is at the forefront of creating and curating high-quality technical content designed to educate and empower aspiring and seasoned professionals in the embedded domain.

Throughout his career, Raj has honed a unique skill set that bridges the gap between deep technical understanding and effective communication. His work encompasses a wide range of educational materials, including in-depth tutorials, practical guides, course modules, and insightful articles focused on embedded hardware and software solutions. He possesses a strong grasp of embedded architectures, microcontrollers, real-time operating systems (RTOS), firmware development, and various communication protocols relevant to the embedded industry.

Raj is adept at collaborating closely with subject matter experts, engineers, and instructional designers to ensure the accuracy, completeness, and pedagogical effectiveness of the content. His meticulous attention to detail and commitment to clarity are instrumental in transforming complex embedded concepts into easily digestible and engaging learning experiences. At Embedded Prep, he plays a crucial role in building a robust knowledge base that helps learners master the complexities of embedded technologies.